Slides: tinyurl.com/riscv-kr-22

Baylibre

# Linux on RISC-V

Drew Fustini <dfustini@baylibre.com>

## \$ whoami

- Linux kernel developer, <u>BayLibre</u>

- embedded software consultancy based in Nice, France, with ~50 engineers around the world <u>contributing to open source projects</u> like Linux, U-Boot, Android and Zephyr

- Board of Directors, <u>BeagleBoard.org Foundation</u>

- Board of Directors, <u>Open Source Hardware Association (OSHWA)</u>

- OSHW Certification Program

- Ambassador, <u>RISC-V International</u>

### RISC-V: a Free and Open ISA

- Started by a computer architecture research group at University of California Berkeley in 2010 led by <u>Krste Asanovic</u>

- V as in the roman numeral five, because it is the 5th RISC instruction set to come out of UC Berkeley

- Free and Open because the <u>specifications</u> are published under an open source license: Creative Commons Attribution 4.0 International

- Volume 1, Unprivileged Spec v. 20191213 [PDF]

- 6

Volume 2, Privileged Spec v. 20211203 [PDF]

#### What is different about RISC-V?

- Simple clean-slate design

- Avoids any dependencies on microarchitecture style (in-order, out-of-order, etc)

- Modular design

- Suitable for everything from microcontrollers to supercomputers

- Stable base

- Base integer ISAs and standard extensions are frozen

- Additions via optional extensions, not new versions

# RISC-V base integer ISAs

RV32I: 32-bit

less than 50 instructions needed!

RV64I: 64-bit

Most important for Linux

RV128I: 128-bit

Future-proof address space

|              | imm[31:12]      |       |     | rd          | 0110111 | LUI   |

|--------------|-----------------|-------|-----|-------------|---------|-------|

|              | imm[31:12]      |       |     | rd          | 0010111 | AUIPC |

|              | m[20 10:1 11 19 | 9:12  |     | rd          | 1101111 | JAL   |

| imm[11:0]    |                 | rs1   | 000 | rd          | 1100111 | JALR  |

| imm[12]10:5] | rs2             | rs1   | 000 | imm[4:1 11] | 1100011 | BEQ   |

| imm[12]10:5  | rs2             | rs1   | 001 | imm[4:1 11] | 1100011 | BNE   |

| imm[12]10:5  | rs2             | rs1   | 100 | imm[4:1[11] | 1100011 | BLT   |

| imm[12]10:5  | rs2             | rs1   | 101 | imm[4:1 11] | 1100011 | BGE   |

| imm[12]10:5  | rs2             | rs1   | 110 | imm[4:1 11] | 1100011 | BLTU  |

| imm[12 10:5] | rs2             | rs1   | 111 | imm[4:1 11] | 1100011 | BGEU  |

| imm[11       | :0]             | rs1   | 000 | rd          | 0000011 | LB    |

| imm 11       | :0]             | rs1   | 001 | rd          | 0000011 | LH    |

| imm[11       | :0]             | rs1   | 010 | rd          | 0000011 | LW    |

| imm[11       | :0              | rs1   | 100 | rd          | 0000011 | LBU   |

| imm[11       | :0]             | rs1   | 101 | rd          | 0000011 | LHU   |

| imm[11:5]    | rs2             | rs1   | 000 | imm[4:0]    | 0100011 | SB    |

| imm[11:5]    | rs2             | rs1   | 001 | imm[4:0]    | 0100011 | SH    |

| imm[11:5]    | rs2             | rsl   | 010 | imm[4:0]    | 0100011 | SW    |

| imm[11       |                 | rs1   | 000 | rd          | 0010011 | ADDI  |

| imm[11       | :0]             | rs1   | 010 | rd          | 0010011 | SLTI  |

| imm[11       | :0]             | rsl   | 011 | rd          | 0010011 | SLTIU |

| imm[11       | :0]             | rs1   | 100 | rd          | 0010011 | XORI  |

| imm[11       | :0]             | rs1   | 110 | rd          | 0010011 | ORI   |

| imm[11       |                 | rs1   | 111 | rd          | 0010011 | ANDI  |

| 0000000      | shamt           | rs1   | 001 | rd          | 0010011 | SLLI  |

| 0000000      | shamt           | rs1   | 101 | rd          | 0010011 | SRLI  |

| 0100000      | shamt           | rs1   | 101 | rd          | 0010011 | SRAI  |

| 0000000      | rs2             | rs1   | 000 | rd          | 0110011 | ADD   |

| 0100000      | rs2             | rs1   | 000 | rd          | 0110011 | SUB   |

| 0000000      | rs2             | rs1   | 001 | rd          | 0110011 | SLL   |

| 0000000      | 182             | rs1   | 010 | rd          | 0110011 | SLT   |

| 0000000      | rs2             | rs1   | 011 | rd          | 0110011 | SLTU  |

| 0000000      | rs2             | rs1   | 100 | rd          | 0110011 | XOR   |

| 0000000      | rs2             | rs1   | 101 | rd          | 0110011 | SRL   |

| 0100000      | rs2             | rs1   | 101 | rd          | 0110011 | SRA   |

| 0000000      | rs2             | rs1   | 110 | rd          | 0110011 | OR    |

| 0000000      | rs2             | rsl   | 111 | rd          | 0110011 | AND   |

| fm pr        |                 | rs1   | 000 | rd          | 0001111 | FENCE |

|              | 00000000000     |       | 000 | 00000       | 1110011 | ECALL |

| 00000000     | 0001            | 00000 | 000 | 00000       | 1110011 | EBREA |

## RISC-V base integer registers

- XLEN defines the register width

- XLEN=32 for RV32L

- XLEN=64 for RV64L

- 32 registers named x0 to x31

- Dedicated PC register

- Base ISA talk by Andrew Waterman explains the instruction encoding scheme

| x0 / zero       |                                                                                |

|-----------------|--------------------------------------------------------------------------------|

| x1              |                                                                                |

| x2              |                                                                                |

| x3              |                                                                                |

| x4              |                                                                                |

| x5              |                                                                                |

| х6              |                                                                                |

| x7              |                                                                                |

| x8              |                                                                                |

| x9              |                                                                                |

| x10             |                                                                                |

| x11             |                                                                                |

| x12             |                                                                                |

| x13             |                                                                                |

| x14             |                                                                                |

| x15             |                                                                                |

|                 |                                                                                |

|                 |                                                                                |

|                 |                                                                                |

|                 |                                                                                |

| 11-0-2011-0-001 |                                                                                |

| 0.000,387,000   |                                                                                |

| U-3000000       |                                                                                |

| 11-0-001100-000 |                                                                                |

|                 |                                                                                |

|                 |                                                                                |

|                 |                                                                                |

| -1100-000       |                                                                                |

|                 |                                                                                |

|                 |                                                                                |

|                 |                                                                                |

|                 |                                                                                |

| XLEN            |                                                                                |

|                 | 0                                                                              |

|                 |                                                                                |

|                 | x1<br>x2<br>x3<br>x4<br>x5<br>x6<br>x7<br>x8<br>x9<br>x10<br>x11<br>x12<br>x13 |

#### RISC-V ABI

- x1 to x31 are all equally general-use registers as far as the processor is concerned

- RISC-V psABI defines standard functions for these registers [PDF]

- s0 to s11 are preserved across function calls

- o argument registers a0 to a7 and the temporary registers t0 to t6 are not

| Register | ABI Name | Description                       | Saver  |

|----------|----------|-----------------------------------|--------|

| x0       | zero     | Hard-wired zero                   | _      |

| x1       | ra       | Return address                    | Caller |

| x2       | sp       | Stack pointer                     | Callee |

| x3       | gp       | Global pointer                    | -      |

| x4       | tp       | Thread pointer                    | -      |

| x5       | t0       | Temporary/alternate link register | Caller |

| x6-7     | t1-2     | Temporaries                       | Caller |

| x8       | s0/fp    | Saved register/frame pointer      | Callee |

| x9       | s1       | Saved register                    | Callee |

| x10-11   | a0-1     | Function arguments/return values  | Caller |

| x12-17   | a2-7     | Function arguments                | Caller |

| x18-27   | s2-11    | Saved registers                   | Callee |

| x28-31   | t3-6     | Temporaries                       | Caller |

#### **RISC-V Standard Extensions**

- M: integer multiply/divide

- A: atomic memory operations

- F, D, Q: floating point, double-precision, quad-precision

- G: "general purpose" ISA, equivalent to IMAFD

- C: compressed instructions conserve memory and cache

- Most Linux distributions target RV64GC

#### Ratified in 2021

- 15 new specifications representing more than 40 extensions

- Vector

- Hypervisor

- Scalar Cryptography

- Bit Manipulation

#### **RISC-V Profiles**

- RISC-V is a highly modular and extensible architecture

- Flexibility to pick and choose what is right for your processor design, but that flexibility creates a large number of possible combinations

- RISC-V Profiles specify a much smaller set of ISA choices that represent the most common use-cases

- RVM for microcontrollers intended to run bare-metal code or an RTOS

- o RVA for application processors designed to run full operating system like Linux

- RISC-V Summit talk by Greg Favor [slides]

#### Learn more about RISC-V

Get up-to-speed quick with the <u>RISC-V Reader</u>

#### Learn more about RISC-V

Textbook: <u>Computer Organization and Design, RISC-V Edition</u>

### RISC-V and Industry

- RISC-V International now controls the specifications: <u>riscv.org</u>

- Non-profit with <u>2,700+ members</u> including companies & universities from 70 countries

- <u>Become a member</u> free of cost to individuals and non-profits!

- RISC-V International YouTube channel has hundreds of talks

- Companies have already shipped billions of RISC-V cores

- Nvidia GPUs have RISC-V cores for system management tasks

- Seagate and Western Digital are using RISC-V cores in storage controllers

### **RISC-V** and Industry

- No ISA licensing fees or royalties

- Avoid legal costs and delays caused by complex licensing agreements

- Freedom to choose microarchitecture implementation

- An open ISA means that everyone has an architecture license

- Freedom to leverage existing open source implementations

- Broad range of open source cores already available from small embedded cores to high-performance out-of-order superscalar designs

### "Is RISC-V an Open Source processor?"

RISC-V is a set of <u>specifications</u> under an <u>open source license</u>

RISC-V implementations can be open source or proprietary

- Open specifications make open source implementations possible

- An open ISA makes it possible to design an open source processor

### RISC-V open source cores

- Academia

- <u>Rocket</u> and <u>BOOM</u> from Berkeley, <u>PULP</u> family of cores from ETH Zurich

- Industry

- <u>SweRV</u> created by Western Digital and now developed by <u>CHIPS Alliance</u>

- OpenHW Group creating proven verified IP like their <u>Core-V</u> designs

- Google <u>OpenTitan</u> silicon root of trust project uses <u>LowRISC</u> <u>lbex</u> core

### RISC-V open source cores

- FPGA soft-cores

- <u>PicoRV32</u>, <u>RVfpga</u>, <u>SERV</u>, and <u>VexRiscV</u>

- FOSSi Foundation

- <u>El Correo Libre</u> monthly newsletter for the latest on open source cores

- Build your own open source SoC with an open source silicon toolchain

- O Google worked with Skywater to open source their 130 nm PDK (process development kit). Google offers free-of-cost MPW (multi-project wafer) runs to open source projects. Learn to design your own using open source design tools with <u>Zero to ASIC</u>.

## RISC-V software ecosystem

- RISC-V already has a well supported <u>software ecosystem</u>

- RISC-V International software committee coordinates efforts of member organizations

- RISC-V extension and feature support

- PLCT Lab led by Wei Wu at ISCAS does a lot of compiler and runtime work

- Operating systems: Linux, BSDs, FreeRTOS, Zephyr

- Toolchains & libraries: gcc, glibc, gdb, binutils, clang/llvm, newlib

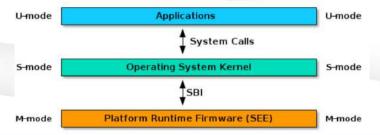

# **RISC-V Privileged Architecture**

- Three privilege modes

- User (U-mode): application

- Supervisor (S-mode): OS kernel

- o Machine (M-mode): firmware

- Environment Call (ECALL) instruction

- Transfer control to a higher privileged mode

- Userspace program (u-mode) uses ECALL to make system call into OS kernel (s-mode)

# Control and Status Registers (CSRs)

- CSR have their own dedicated instructions to read and write

- CSR are specific to a mode (e.g. m-mode and s-mode)

- Machine Status (mstatus) is an important CSR

| Bits    | Field Name | Description                          |  |

|---------|------------|--------------------------------------|--|

| 0       | UIE        | User Interrupt Enable                |  |

| 1       | SIE        | Supervisor Interrupt Enable          |  |

| 2       | Reserved   |                                      |  |

| 3       | MIE        | Machine Interrupt Enable             |  |

| 4       | UPIE       | User Previous Interrupt Enable       |  |

| 5       | SPIE       | Supervisor Previous Interrupt Enable |  |

| 6       | Reserved   |                                      |  |

| 7       | MPIE       | Machine Previous Interrupt Enabler   |  |

| 8       | SPP        | Supervisor Previous Privilege        |  |

| [10:9]  | Reserved   |                                      |  |

| [12:11] | MPP        | Machine Previous Privilege           |  |

| Bits    | Field Name | Description                             |

|---------|------------|-----------------------------------------|

| [14:13] | FS         | Floating Point State                    |

| [16:15] | XS         | User Mode Extension State               |

| 17      | MPRIV      | Modify Privilege (access memory as MPP) |

| 18      | SUM        | Permit Supervisor User Memory Access    |

| 19      | MXR        | Make Executable Readable                |

| 20      | TVM        | Trap Virtual memory                     |

| 21      | TW         | Timeout Wait (traps S-Mode wfi)         |

| 22      | TSR        | Trap SRET                               |

| [23:30] | Reserved   |                                         |

| [31]    | SD         | State Dirty (FS and XS summary bit)     |

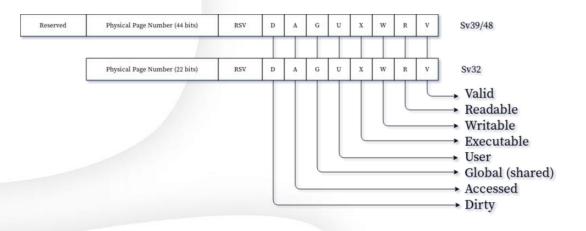

# **RISC-V Virtual Memory**

- satp CSR (Supervisor Address Translation and Protection) controls supervisor-mode address translation and protection

- Sv32: 3 level page table

- Sv39: 3 level page table

- Sv48: 4 level page table

- Sv57: 5 level page table

# **RISC-V Trap Handling**

- Exceptions occur synchronously

- Interrupts occur asynchronously

- <x>cause CSR indicates which interrupt or exception occurred

- o mcause for m-mode / scause for s-mode

- Corresponding bit is set in <x>E/IP CSR

| Trap<br>code[62:0] | Exception (Cause[MSB]=0)    | Interrupt (Cause[MSB]==1)     |  |

|--------------------|-----------------------------|-------------------------------|--|

| 0                  | Instruction addr misaligned | User Software Interrupt       |  |

| 1                  | Instruction access fault    | Supervisor Software Interrupt |  |

| 2                  | Illegal instruction         | Reserved                      |  |

| 3                  | Breakpoint                  | Machine Software Interrupt    |  |

| 4                  | Load address misaligned     | User Timer Interrupt          |  |

| 5                  | Load access fault           | Supervisor Timer Interrupt    |  |

| 6                  | Store/AMO addr misaligned   | Reserved                      |  |

| 7                  | Store/AMO access fault      | Machine Timer Interrupt       |  |

| 8                  | Environment call            | User External Interrupt       |  |

| 9                  |                             | Supervisor External Interrupt |  |

| 10                 | Reserved                    | Reserved                      |  |

| 11                 |                             | Machine External Interrupt    |  |

| 12                 | Instruction page fault      | - Reserved                    |  |

| 13                 | Load page fault             |                               |  |

| 14                 | Reserved                    |                               |  |

| 15                 | Store/AMO page fault        |                               |  |

| >=16               | Reserved                    | Reserved                      |  |

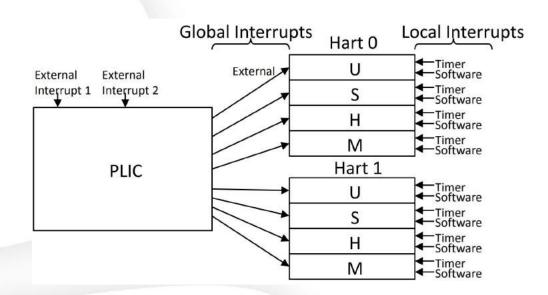

#### What is a Hart?

- Hart is a hardware thread

- Each RISC-V core contains an independent instruction fetch unit

- A RISC-V core with multi-threading (SMT) would contain multiple harts

- Each hart is a processor from the perspective of Linux

- o Imagine a RISC-V laptop which has 2 cores with 2 harts per core

- Linux would see 4 processors

# **RISC-V Interrupts**

- Local per-hart interrupts

- <u>CLINT</u> (Core Local Interruptor)

- <u>CLIC</u> (Core Local Interrupt Controller)

- Global interrupts

- PLIC (Platform Level Interrupt Controller)

# **Advanced Interrupt Architecture (AIA)**

- Developed on the AIA SIG mailing list: <u>tech-aia</u>

- APLIC (Advanced Platform-Level Interrupt Controller) replaces PLIC

- Adds IMSIC (Incoming Message-Signaled Interrupt Controller) for PCIe

- AIA is complimented by <u>ACLINT (Advanced Core Local Interruptor)</u>

- Developed on the <u>tech-unixplatformspec</u> mailing list

- Backwards compatible with the SiFive CLINT but restructured to be more efficient

- RISC-V Summit talk by Anup Patel and John Hauser [slides]

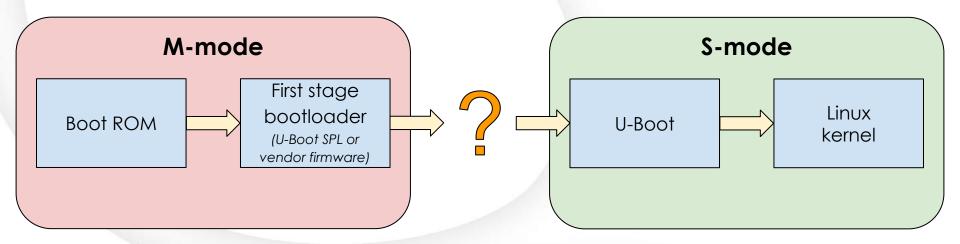

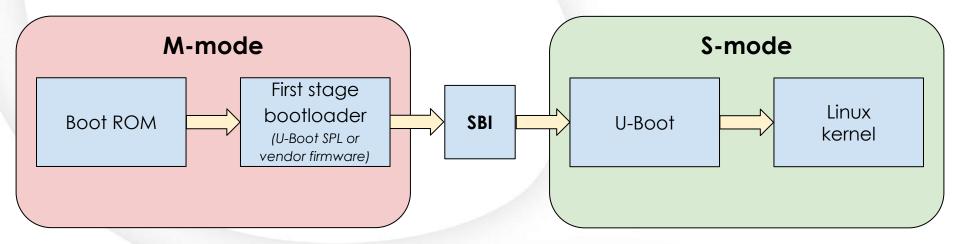

#### **RISC-V Boot Flow**

#### **RISC-V Boot Flow**

# **Supervisor Binary Interface (SBI)**

- Non-ISA RISC-V specification

- This means it does not add or modify and RISC-V instructions

- The calling convention between S-mode and M-mode

- Allows supervisor-mode (s-mode) software like the Linux to be portable across RISC-V implementations by abstracting platform specific functionality

# **Supervisor Binary Interface (SBI)**

- Required by the <u>UNIX-Class Platform Specification</u>

- Mailing list: <u>tech-unixplatformspec</u>

- This will be replaced by the upcoming <u>RISC-V Platform Specification</u>

- Small core along with a set of optional modular extensions

- Base extension query basic information about the machine

- o Timer extension program the clock for the next event

- IPI extension send an inter-processor interrupt to harts defined in mask

• RFENCE extension - instructs remote harts to execute FENCE.I instruction

#### **SBI Extensions**

- Hart State Management (HSM)

- S-mode can request to stop, start or suspend a hart

- SBI implementation called by some other hart stopping hart STOP PENDING START PENDING sbi\_hart\_stop() called by SBI implementation starting hart STARTED sbi hart suspend() SBI implementation called by hart itself resuming hart RESUME PENDING SUSPEND\_PENDING Hart recieved SBI implementation an interrupt or

- System Reset

- Supervisor-mode software can request system-level reboot or shutdown

- Performance Monitoring Unit

- Interface for supervisor-mode to configure and use the RISC-V hardware performance counters with assistance from the machine-mode

o <u>"Performance Monitoring in RISC-V using perf"</u> by Atish Patra

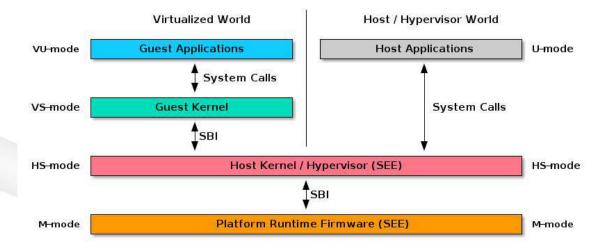

### Hypervisor extension

- Hypervisor Supervisor mode (HS-mode) where host kernel runs

- Virtualized Supervisor mode (VS-mode) where the guest kernel runs

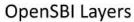

# <u>OpenSBI</u>

- Open source implementation of SBI

- Core library

- Platform specific libraries

- Full reference firmware for some platforms

- Provides runtime services to S-mode software

- SBI extensions present on a platform define the available runtime services

- Unimplemented instructions will trap and OpenSBI can emulate

# OpenSBI Generic Platform

- No need to add code to OpenSBI for each new platform

- First-stage bootloader, like U-Boot SPL, is expected to pass a Device Tree to OpenSBI which describes all the platform specific functionality

- The same OpenSBI binary can be used across platforms

- Many RISC-V boards and emulators now use Generic Platform

- Linux distros do not need to ship a different OpenSBI build for each board

# OpenSBI Domain Support

- An <u>OpenSBI domain</u> is a system-level partition of underlying hardware having its own memory regions and HARTs

- Talk by Anup Patel

### **UEFI Support**

- UEFI is a standard interface between firmware and operating systems,

and it is used on most x86 and arm64 platforms

- <u>U-Boot</u> and <u>TianoCore EDK2</u> both have UEFI implementations on RISC-V

- Grub2 can be used as an UEFI payload on RISC-V

- <u>UEFI support for RISC-V</u> added in <u>Linux 5.10</u>

### **UEFI Support**

- Boot hart ID is known only at boot and it is needed before ACPI tables or DT properties can be parsed

- Hart ID is passed in the a0 register on non-UEFI systems, but the UEFI application calling conventions do not allow this

- RISC-V EFI Boot Protocol allows the OS to discover the boot hart ID

- The <u>public review</u> process has completed, and Sunil V L has added support to the Linux kernel for <u>RISCV\_EFI\_BOOT\_PROTOCOL</u>

- Goal is to support "off-the-shelf" software by standardizing the interface between hardware platforms and operating systems

- Created by the Platforms Horizontal Subcommittee (HSC)

- Bi-weekly meetings chaired by <u>Kumar Sankaran</u>

- Mailing list: <u>tech-unixplatformspec</u>

- Platforms talk at <u>RISC-V Summit 2021</u>

- o Philipp Tomsich, Chair of Software HSC, and Mark Himelstein CTO RISC-V International

#### OS-A Platform

- o "A" as in application, this is a category of platforms that support full OS like Linux

- OS-A Common Requirements

- OS-A Embedded Platform

- OS-A Server Platform

#### RVM-CSI Platform

Bare-metal applications or RTOS running on RISC-V microcontrollers

CSI is common software interface; goal is to ease porting, not binary compatibility

- OS-A common requirements for Embedded and Server

- Must comply with the RVA22U and RVA22S ISA profiles as defined in <u>RISC-V ISA Profiles</u>

- Common requirements for Debug, Timers, Interrupt Controllers

- Requires serial console with UART 8250 or UART 16550

- Requirements for runtime services such as SBI extensions

- Software components must comply with the <u>RISC-V Calling Convention specification</u>

and the <u>RISC-V ELF specification</u>

- OS-A Embedded Platform

- Target might be a single board computer or mobile device

- PMU counters and events for performance monitoring

- Boot process must comply with <u>Embedded Base Boot Requirements (EBBR) spec</u>

- EBBR requires a subset of the UEFI spec which U-Boot has implemented

- Device Tree (DT) is the required mechanism for the hardware discovery and config

- GPT partitioning required for shared storage

- OS-A Server Platform

- Goal is for an enterprise Linux distro like RHEL to "just work" on server-class hardware that complies with this

- System peripheral requirements like PCIe, watchdog timer, system date/time

- RAS (Reliability, Availability, and Serviceability) requirements like ECC RAM

- ACPI is the required mechanism for the hardware discovery and configuration

- Must comply with the <u>RISC-V ACPI Platform Requirements Specification</u>

- Defines mandatory ACPI tables and objects for RISC-V server platforms

- New tables are needed for RISC-V

- RISC-V Hart Capabilities Table (RHCT)

- RISC-V Timer Description Table (RTDT)

- More details in '<u>ACPI for RISC-V: Enabling Server Class Platforms</u>'

- Sunil V L from Ventana Microsystems at RISC-V Summit [slides]

#### RISC-V emulation in QEMU

- Support for <u>RISC-V in mainline QEMU</u>

- Boots 32-bit and 64-bit mainline Linux kernel

- Machine configs to boot same binaries as some RISC-V dev boards

- Supports the new Hypervisor and Vector extensions

#### RISC-V in the Linux kernel

- Initial port by Palmer Dabbelt was merged into Linux 4.15 back in 2018

- "It's a fun, friendly, and still pretty small community" Björn Töpel [1]

- Palmer continues to maintain the <u>riscv tree</u>

- Development happens on the <u>linux-riscy mailing list</u>

- View the archive on <u>lore.kernel.org</u>

- IRC: #riscv on libera.chat

```

linux-riscv.lists.infradead.org archive mirror

search help / color / mirror / Atom feed

[PATCH 0/2] riscv: implement Zichom-based CMO instructions + the t-head variant

2022-04-17 17:35 UTC (10+ messages)

[PATCH VZ 0/3] riscv: atomic: Optimize AMO instructions usage

2022-04-17 6:45 UTC (10+ messages)

[PATCH V2 1/3] riscv: atomic; Cleanup unnecessary definition

[PATCH V2 2/3] riscv: atomic: Optimize acquire and release for AMO operations

PATCH V2 3/31 riscv: atomic: Optimize memory barrier semantics of LRSC-pairs

[PATCH v3 0/7] Generic Ticket Spinlocks

2022-04-17 2:44 UTC (14+ messages)

[PATCH v3 1/7] asm-generic: ticket-lock: New generic ticket-based spinlock

[PATCH v3 2/7] asm-generic: qspinlock: Indicate the use of mixed-size atomics

PATCH v3 3/7] asm-generic: grwlock: Document the spinlock fairness requirements

[PATCH v3 4/7] openrisc: Move to ticket-spinlock

PATCH v3 5/71 RISC-V: Move to generic spinlocks

PATCH v3 6/71 RISC-V: Move to gueued RW locks

[PATCH v3 7/7] csky: Move to generic ticket-spinlock

```

```

pdp7@x1:~/linux$ ./Documentation/features/list-arch.sh riscv | ack --passthru TODO

# Kernel feature support matrix of the 'riscv<u>' architecture:</u>

core/ cBPF-JIT

HAVE CBPF JIT # arch supports cBPF JIT optimizations

core/ eBPF-JIT

: ok

HAVE EBPF JIT # arch supports eBPF JIT optimizations

core/ generic-idle-thread : ok |

GENERIC SMP IDLE THREAD # arch makes use of the generic SMP idle thread facility

core/ jump-labels

HAVE ARCH JUMP LABEL # arch supports live patched, high efficiency branches

: ok

core/ thread-info-in-task : ok |

THREAD INFO IN TASK # arch makes use of the core kernel facility to embedd thread info in task struct

core/ tracehook

: ok

HAVE_ARCH_TRACEHOOK # arch supports tracehook (ptrace) register handling APIs

debug/ debug-vm-pgtable : ok |

ARCH HAS DEBUG VM PGTABLE # arch supports pgtable tests for semantics compliance

ARCH HAS GCOV PROFILE ALL # arch supports whole-kernel GCOV code coverage profiling

debug/ gcov-profile-all

: ok

debug/ KASAN

: ok

HAVE ARCH KASAN # arch supports the KASAN runtime memory checker

debug/ kcov

: ok

ARCH HAS KCOV # arch supports kcov for coverage-guided fuzzing

debug/ kgdb

: ok |

HAVE ARCH KGDB # arch supports the kGDB kernel debugger

debug/ kmemleak : ok |

HAVE DEBUG KMEMLEAK # arch supports the kernel memory leak detector

debug/ kprobes

: ok

HAVE KPROBES # arch supports live patched kernel probe

debug/ kprobes-on-ftrace : ok |

HAVE KPROBES ON FTRACE # arch supports combined kprobes and ftrace live patching

debug/ kretprobes

: ok

HAVE KRETPROBES # arch supports kernel function-return probes

TODO

HAVE OPTPROBES # arch supports live patched optprobes

debug/ optprobes

: ok

debug/ stackprotector

HAVE STACKPROTECTOR # arch supports compiler driven stack overflow protection

debug/ uprobes

ARCH SUPPORTS UPROBES # arch supports live patched user probes

TODO

debug/ user-ret-profiler

HAVE USER RETURN NOTIFIER # arch supports user-space return from system call profiler

io/ dma-contiguous

HAVE DMA CONTIGUOUS # arch supports the DMA CMA (continuous memory allocator)

locking/ cmpxchg-local

: TODO

HAVE CMPXCHG LOCAL # arch supports the this cpu cmpxchq() API

locking/ lockdep

LOCKDEP SUPPORT # arch supports the runtime locking correctness debug facility

TODO

locking/ queued-rwlocks

ARCH USE QUEUED RWLOCKS # arch supports queued rwlocks

locking/ queued-spinlocks

TODO

ARCH USE QUEUED SPINLOCKS # arch supports queued spinlocks

: ok

HAVE REGS AND STACK ACCESS API # arch supports kprobes with perf events

perf/ kprobes-event

HAVE PERF REGS # arch supports perf events register access

perf/ perf-regs

perf/ perf-stackdump

HAVE PERF USER STACK DUMP # arch supports perf events stack dumps

sched/ membarrier-sync-core : TODO

ARCH HAS MEMBARRIER SYNC CORE # arch supports core serializing membarrier

sched/ numa-balancing

: ok

ARCH SUPPORTS NUMA BALANCING # arch supports NUMA balancing

seccomp/ seccomp-filter

HAVE ARCH SECCOMP FILTER # arch supports seccomp filters

: ok

time/ arch-tick-broadcast : ok

ARCH HAS TICK BROADCAST # arch provides tick broadcast()

: ok |

time/ clockevents

!LEGACY TIMER TICK # arch support generic clock events

: ok |

HAVE CONTEXT TRACKING # arch supports context tracking for NO HZ FULL

time/ context-tracking

time/ irq-time-acct

HAVE IRO TIME ACCOUNTING # arch supports precise IRO time accounting

TODO

time/ virt-cpuacct

HAVE VIRT CPU ACCOUNTING # arch supports precise virtual CPU time accounting

vm/ batch-unmap-tlb-flush: TODO |

ARCH WANT BATCHED UNMAP TLB FLUSH # arch supports deferral of TLB flush until multiple pages are unmapped

ARCH HAS ELF RANDOMIZE # arch randomizes the stack, heap and binary images of ELF binaries

vm/ ELF-ASLR

: ok |

HAVE_ARCH_HUGE_VMAP # arch supports the arch_vmap_pud_supported() and arch_vmap_pmd_supported() VM APIs

vm/ huge-vmap

TODO

vm/ ioremap prot

TODO

HAVE IOREMAP PROT # arch has ioremap prot()

TODO

vm/ PG_uncached

ARCH USES PG UNCACHED # arch supports the PG uncached page flag

vm/ pte special

: ok

ARCH HAS PTE SPECIAL # arch supports the pte special()/pte mkspecial() VM APIs

VM/ THP

HAVE ARCH TRANSPARENT HUGEPAGE # arch supports transparent hugepages

```

## Recently added to Linux

- KVM RISC-V support by Anup Patel added in <u>Linux 5.16</u>

- Add KVM support for the Hypervisor specification

- SBI SRST extension support by Anup Patel added in <u>Linux 5.17</u>

- Support for the SBI SRST (system reset) extension which allows systems that do not have an explicit driver in Linux to reboot

## New in Linux 5.18

- Add Sv57 page table support by Qinglin Pan

- use 5-level page table to support <u>Sv57</u> which expands the virtual address space to

57 bits (128 petabytes)

- Improve RISC-V Perf support by Atish Patra

- Recent talk: <u>Perf on RISC-V: The Past, the Present and the Future</u> (<u>slides</u>)

## New in Linux 5.18

- RISC-V CPU Idle support by Anup Patel

- cpuidle and suspend drivers now support the SBI HSM extension

- <u>Provide framework for RISC-V ISA extensions</u> by Atish Patra

- Linux was no longer correctly parsing the RISC-V ISA string as the number of RISC-V extensions has grown and extension names are no longer a single character

- This series implements a generic framework to parse multi-letter ISA extensions.

- Based on initial work by <u>Tsukasa Ol</u>

## Coming in Linux 5.19...

- RISC-V Patches for the 5.19 Merge Window, Part 1 Palmer (2022-05-31)

- Support for page-based memory attributes <we'll dive into that topic in a few slides>

- Support for running rv32 binaries on rv64 systems via the compat subsystem

- Support for kexec\_file()

- Support new generic ticket-based spinlocks, which allows us to also move to grwlock

- A handful of cleanups and fixes, include some larger ones around atomics and XIP

- Part 2? Follow <u>linux-riscv</u> and look at Palmer's <u>riscv/for-next</u> branch

## Work in progress

- [PATCH v10 00/16] riscv: Add vector ISA support by Greentime Hu

- Vector ISA support based on the ratified Vector 1.0 extension

- o Defines new structure \_\_riscv\_v\_state in struct thread\_struct to save/restore the vector related registers. It is used for both kernel space and user space.

- [PATCH v6 0/7] RISC-V IPI Improvements by Anup Patel

- Traditionally, RISC-V S-mode software like the Linux kernel calls to into M-mode runtime firmware like OpenSBI to issue IPIs (inter-processor interrupts)

- 6

AIA (advanced interrupt architecture) provides the ability for S-mode to issue IPIs without any assistance from M-mode. This improves efficiency.

## Work in progress

- [PATCH v4 0/4] Add Sstc extension support by Atish Patra

- Traditionally, an SBI call is necessary to generate timer interrupts as S-mode does not have access to the M-mode time compare registers.

- This results in significant latency for the kernel to generate timer interrupts at kernel

- For virtualized environments, it's even worse as the KVM handles the SBI call and uses a software timer to emulate the time compare register.

- Sstc extension allows kernel to program a timer and receive interrupt without supervisor execution environment (M-mode/HS mode) intervention.

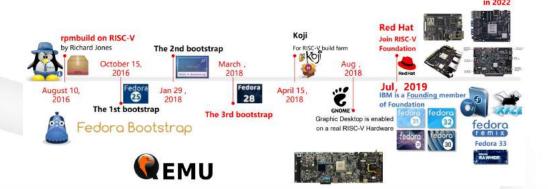

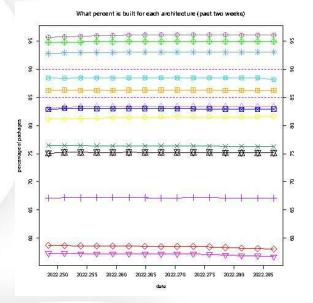

## Linux distro: Fedora

- Aims to provide a complete Fedora experience on RISC-V

- <u>Talk by Wei Fu</u>, RISC-V Ambassador and Red Hat engineer [<u>slides</u>]

- <u>Installation instructions</u> for QEMU and RISC-V dev boards

# Linux distro: **Debian**

- riscv64 is port of Debian to RISC-V

- "a port in Debian terminology means to provide the software normally available in the Debian archive (over 20,000 source packages) ready to install and run"

- 95% of packages are built for RISC-V

- The Debian port uses RV64GC as the hardware baseline and the <u>lp64d ABI</u>

# Linux distro: Ubuntu

- riscv64 supported since the release of Ubuntu 20.04 LTS.

- Ubuntu 22.04 pre-installed SD-card image for SiFive boards and QEMU

- Starting with Ubuntu 22.04, <u>a server install image</u> is made available to install Ubuntu on NVMe drive of the SiFive Unmatched board

#### Linux distros

- OpenSuSE

- RISC-V support is still under development with Tumbleweed images for some boards

- Arch Linux

- Community effort has 95% of core packages building for RISC-V

- Gentoo

- riscv64 stages are available on the Gentoo download page

### OpenEmbedded and Yocto

- meta-riscv: general hardware-specific BSP overlay for RISC-V devices

- works with different OpenEmbedded/Yocto distributions and layer stacks

- Supports both <u>QEMU</u> and <u>RISC-V dev boards</u>

#### **BuildRoot**

- RISC-V port is now <u>supported</u> in the upstream <u>BuildRoot project</u>

- "Embedded Linux from scratch in 45 minutes (on RISC-V)"

- Tutorial by Michael Opdenacker at FOSDEM 2021

- Use Buildroot to compile OpenSBI, U-Boot, Linux and BusyBox

- Boot the system in QEMU

#### SiFive Freedom Unleashed

- Launched in 2018 as first Linux-capable RISC-V dev board

- Exciting to see Fedora GNOME desktop on RISC-V

- \$999 was too expensive for widespread adoption

- FU540 SoC chip was never sold separately

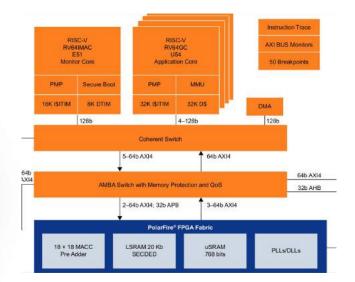

## Microchip PolarFire SoC

- Same RISC-V cores as the SiFive FU540 SoC but adds a FPGA fabric

- FPGA with 25k to 460k logic elements (LEs)

- Supports DDR4 and PCIe Gen2

- Full commercial product family

- Parts will be available from <u>distributors</u>

- Microchip Icicle dev board (\$499)

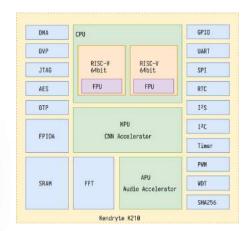

## Kendryte K210

- 400 MHz dual core RV64GC

- 8MB SRAM but no DRAM

- Dev boards starting at \$14

- Upstream support in <u>Linux</u> and <u>u-boot</u>

- <u>Buildroot</u> support by Damien Le Moal can create a busybox-based rootfs

#### **SiFive Unmatched**

- SiFive Freedom FU740 SoC

- 4x U74 RV64GC application cores

- Mini-ITX PC form factor

- o 16GB DDR4, 4x USB 3.2, one x16 PCle slot

- M.2 for NVMe SSD and WiFi/Bluetooth

- Shipped in 2021 for <u>\$665</u>

- Discontinued in 2022 to focus on next-gen

#### T-Head XuanTie C910

- <u>T-Head</u> ("píng tóu gē") is part of Alibaba

- High performance RV64GC with up 16 cores

- o 12-stage pipeline, out-of-order, multi-issue architecture

- comparable to Arm Cortex-A73

- 2 core 'ICE' SoC made in low qty for evaluation

- T-Head ported <u>Android 10 (AOSP) to RISC-V</u> and showed a demo on the ICE in early 2021

### Porting Android to RISC-V

- Mao Han presented why and how Alibaba

T-Head ported Android to RISC-V (jump to 4:32)

- PDF of slides

- Update on Android 12 from April (jump to <u>13:23</u>)

- PDF of slides

- How Alibaba is Porting RISC-V to the Android OS blog post with more technical details

#### T-Head RVB-ICE dev board

- 'ICE' SoC featuring dual C910 core at 1.2GHz

- 4GB LPDDR4, 16GB eMMC, 7 inch touchscreen, WiFi, Gigabit Ethernet

- Produced in limited quantity and available on <u>AliExpress for \$399</u>

## RISC-V Android SIG (Special Interest Group)

- GitHub organization <u>riscv-android-src</u> "contains all the modified AOSP(Android open source project) repositories with RISC-V support"

- Instruction to build and run <u>Android 12 on RISC-V</u>

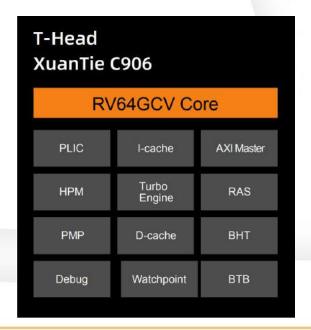

#### T-Head XuanTie C906

• single-core RV64GC, only up to 1GHz, simpler 5-stage in-order pipeline

#### **Allwinner D1 SoC**

mass production low cost SoC with a single T-Head C906 core at 1 GHz

智能语音

DDR2/DDR3, up to 2 GB SD3.0/eMMC 5.0 SPI Nor/Nand Flash

#### DSF

32 KB I-cache + 32 KB D-cache 64 KB I-ram + 64 KB D-ram

#### Video Decoder

4K@30fps H265/H264 MPEG/JPEG/VC1/MJPEG

#### **Display Engine**

Allwinner SmartColor2.0, DI, G2D

#### Video OUT

HDMI, MIPI, LVDS, LCD, CVBS

#### Video in

CSI, CVBS

#### Audio

CODEC, I2S/PCM, DMIC

#### Connectivity

USB2.0, SDIO 3.0, 1000M EMAC

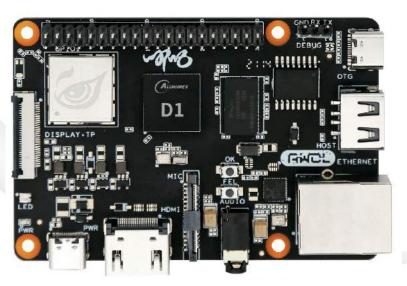

#### <u>Allwinner Nezha D1 dev board</u>

Official D1 board made by Allwinner Online, \$115 bundle on AliExpress

- Main control: Allwinner D1 C906 RISC-V 1GHz

- DRAM: DDR3 1GB/2GB

- Storage: Onboard 256MB spi-nand, support USB external U disk and SD card to expand storage

- · Network: Support Gigabit Ethernet, support 2.4G WiFi and Bluetooth, onboard antenna

- Display: Support MIPI-DSI+TP screen interface, support HDMI output, support SPI screen

- Audio: Microphone daughter board interface \* 1, 3.5mm headphone jack \* 1 (CTIA)

- Board size: length 85mmwidth 56mmthickness 1.7mm

- · PCB layer: 6 layers

- . Support Tina Linux, based on Linux 5.4 kernel

## **RISC-V Developer Boards**

- Initiative from RISC-V International to get Linux-capable boards into the hands of open source developers

- Launched in 2021 with the Allwinner D1 Nezha and SiFive Unmatched

- Fill out <u>this form</u> to apply

- Need to be RISC-V International member (or part of a member organization),

but remember that individuals can join RISC-V International free of cost

- Explain why you are interested in RISC-V and what you plan to do with dev board

To improve your chances, don't overestimate your hardware requirements like RAM

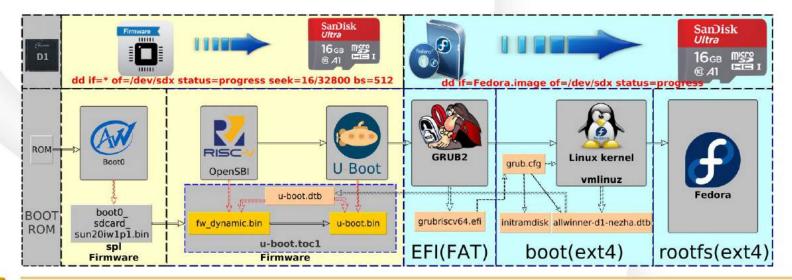

## Allwinner D1 open source community

- <u>linux-sunxi</u>: strong open source community for Allwinner SoCs

- o <u>D1 wiki page</u> and <u>Allwinner Nezha board wiki page</u>

- Telegram group: <u>Mainline Linux for D1</u> (190 members)

- <u>Samuel Holland</u> has been working on getting mainline to run

- U-Boot SPL: <a href="https://github.com/smaeul/sun20i d1 spl">https://github.com/smaeul/sun20i d1 spl</a>

- OpenSBI: <a href="https://github.com/smaeul/opensbi">https://github.com/smaeul/opensbi</a>

- U-Boot: <a href="https://github.com/smaeul/u-boot/tree/d1-wip">https://github.com/smaeul/u-boot/tree/d1-wip</a>

Linux: <a href="https://github.com/smaeul/linux/tree/riscv/d1-wip">https://github.com/smaeul/linux/tree/riscv/d1-wip</a>

#### Fedora on Allwinner D1

Wei Fu has created a Fedora "Rawhide" image for the Allwinner D1

Nezha dev board that includes the XFCE desktop environment

#### Lichee RV-Nezha CM

- Allwinner D1 with DDR3 RAM of either

512MB (\$22) or 1GB (\$32)

- 1.14" SPI LCD, USB Type-C OTG, uSD

- <u>Lichee RV Dock</u>: HDMI out, USB-A host port, WiFi+BT, mic, audio out

- <u>Lichee RV 86 Panel</u>: 8 inch screen

- More details on <u>sunxi wiki</u>

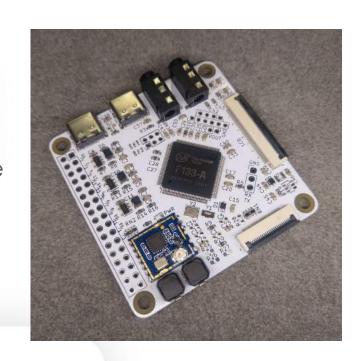

## Xassette Asterisk

- Allwinner F133 combines the Allwinner D1 with 64MB DDR2 in a single package

- Board design published as <u>Open Source</u>

<u>Hardware</u> under the <u>CERN OHL-w v2</u> licence

- Designed with <u>KiCad</u> (open source CAD sw)

- Not available commercially but possible to be hand assembled by hobbyists

# MangoPi-Nezha MQ

- Allwinner F133 (also known as D1s)

- WiFi, USB Type C, mic, audio out

- DSI and RGB display connectors

- Open source hardware: <u>KiCad files on GitHub</u>

- \$39 on Crowd Supply

# Allwinner D1 mainline Linux support

- Allwinner reused peripheral IP from their existing ARM SoCs and the Linux kernel already has drivers for most of them

- T-Head cores like C910 and C906 do have some non-standard functionality for performance but it's not needed to boot

- o Instructions to accelerate I-cache and TLB synchronization

- T-Head MMU has a non-standard 'enhanced' mode that is needed to support DMA with devices on non-coherent interconnects

Linux needs to enable that 'enhanced' MMU mode to function properly

## How to handle non-coherent interconnects?

- The original RISC-V Privileged spec stated that "the use of hardware-incoherent regions is discouraged due to software complexity, performance, and energy impacts"

- However, non-coherent interconnects are important for low cost SoCs

- T-Head designed the C9xx cores in 2019, and there were no RISC-V extensions that provided ability to handle non-coherent devices

### T-Head PTE format

T-Head used bits in the PTE (Page Table Entry) to specify memory type

```

| 63 | 62 | 61 | 60 | 59-8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0

SO C B SH RSW D A G U X W R V

^ ^ ^ ^

BIT(63): SO - Strong Order

BIT(62): C - Cacheable

BIT(61): B - Bufferable

BIT(60): SH - Shareable

0000 - NC Weakly-ordered, Non-cacheable, Non-bufferable, Non-shareable

0111 - PMA Weakly-ordered, Cacheable, Bufferable, Shareable

1000 - IO Strongly-ordered, Non-cacheable, Non-bufferable, Non-shareable

```

... but those bits were already marked reserved in RISC-V priv spec

# Page-Based Memory Types extension

- Svpbmt proposed by <u>Virtual Memory TG</u> and ratified at the end of 2021

- "S" = supervisor-mode (privileged architecture), "v" for virtual memory

# Svpbmt support in Linux

- [PATCH v10 00/12] riscv: support for Sypbmt and D1 memory types

- by Heiko Stuebner based on initial work by Alibaba kernel engineer Guo Ren

- Implements the official RISC-V Sypbmt extension

- The standard Svpbmt and custom T-Head PTE formats both use the highest bits to determine memory type but the encoding and semantics are different

- The custom T-Head PTE format is supported through boot-time code patching using the <u>Linux Alternatives Framework</u>

- Expected to land in Linux 5.19 as it is in Palmer's pull request

# **Cache Management Operations**

- Instructions to manage cache are important for SoCs which that lack cache coherent interconnects

- <u>Zicbom</u> extension ("Z" prefix means Unpriv spec) was ratified at the end of 2021, and it defines cache-block management (CBO) instructions:

- CBO.CLEAN guarantee store by hart can be read from mem by non-coherent device

- CBO.INVAL guarantee hart can load data written to memory by non-coherent device

- o CBO.FLUSH guarantees both

<u>Support for Non-Coherent I/O Devices in RISC-V</u> from RV Summit [slides]

# **CMO** support in Linux

- <u>riscv: implement Zicbom-based CMO instructions + the t-head variant</u> by Heiko Stuebner

- Implements Zicbom-extension to handle cache clean, invalidate, flush

```

* cbo.clean rs1

* | 31 - 20 | 19 - 15 | 14 - 12 | 11 - 7 | 6 - 0 |

* 0...01 rs1 010 00000 0001111

*

* cbo.flush rs1

* | 31 - 20 | 19 - 15 | 14 - 12 | 11 - 7 | 6 - 0 |

* 0...10 rs1 010 00000 0001111

*

* cbo.inval rs1

* | 31 - 20 | 19 - 15 | 14 - 12 | 11 - 7 | 6 - 0 |

* 0...00 rs1 010 00000 0001111

#define CBO_INVAL_A0 ".long 0x15200F"

#define CBO_CLEAN_AO ".long 0x25200F"

#define CBO_FLUSH_AO ".long 0x05200F"

```

# **CMO** support in Linux

T-Head implemented custom cache instructions before Zicbom existed

```

* dcache.ipa rs1 (invalidate, physical address)

* | 31 - 25 | 24 - 20 | 19 - 15 | 14 - 12 | 11 - 7 | 6 - 0 |

0000001

01010

rs1

000

00000 0001011

* dache.iva rs1 (invalida, virtual address)

0000001

00110

000

00000 0001011

* dcache.cpa rs1 (clean, physical address)

* | 31 - 25 | 24 - 20 | 19 - 15 | 14 - 12 | 11 - 7 | 6 - 0 |

0000001

01001

rs1

000

dcache.cva rs1 (clean, virtual address)

0000001

00100

000

00000 0001011

* dcache.cipa rs1 (clean then invalidate, physical address)

* | 31 - 25 | 24 - 20 | 19 - 15 | 14 - 12 | 11 - 7 | 6 - 0 |

0000001 01011

000

00000 0001011

rs1

* dcache.civa rs1 (... virtual address)

* 0000001

00111

000

00000 0001011

#define THEAD INVAL A0 ".long 0x0265000b"

#define THEAD CLEAN A0 ".long 0x0245000b"

#define THEAD FLUSH A0 ".long 0x0275000b"

```

# **CMO** support in Linux

- While the Zicbom and T-Head instructions are different, they provide the same functionality, so the T-Head variant handled with the existing alternatives mechanism

- Allwinner D1 needs these cache instructions for peripherals like MMC (SD card), USB, and Ethernet to work

- Unfortunately, these patches use pre-coded CMO instructions and Palmer would prefer that Linux support wait until the instructions are added to acc and binutils

# Allwinner D1 IOMMU support

- [PATCH 0/5] iommu/sun50i: Allwinner D1 support by Samuel Holland

- IOMMU is not needed for boot

- Optional feature for the display engine and video decoder

- Without IOMMU support, video/frame buffers have to be contiguous in physical memory, and that requires the user to know how much memory to reserve for them at boot

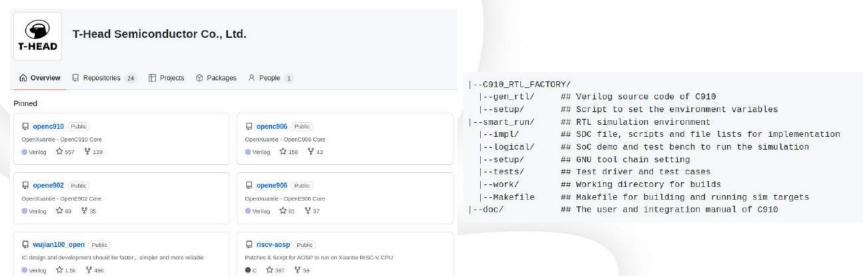

## T-Head released RISC-V cores as open source!

OpenE902, OpenE906, OpenC906, and OpenC910 cores on GitHub under permissive Apache 2.0 licence

# XiangShan (香山)

- open source high-performance RISC-V processor project from the Chinese Academy of Science

- RISC-V Summit 2021 talk by Professor Yungang Bao (slides)

- "Contribute to XiangShan and realize your ideas on real chips! The open-source

XiangShan will be taped-out every ~6 months"

- Nanhu is the 2nd generation microarchitecture

- Target: 2GHz@14nm, SPEC CPU2006 20 marks; 7.81 CoreMark/MHz

#### RISC-V Lab

- PLCT Lab at Chinese Academy of Sciences

- Status report from lab director Wei Wu

- Continuous Integration (CI) for open source software projects on RISC-V hardware

- 70+ SiFive Unmatched boards

- o 100+ Allwinner Nezha D1 boards

- Open source devs can request access

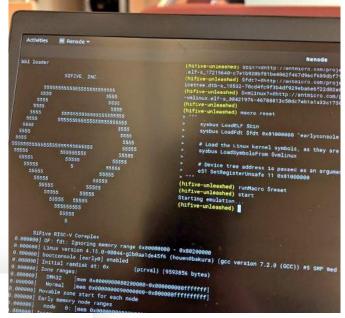

# No hardware? Try <u>Renode!</u>

- Emulate physical hardware systems including CPU, peripherals, sensors, and networking

- Run the same binaries as the real hardware for over <u>30 supported dev boards</u>

- Microchip PolarFire SoC Icicle Kit

- Kendryte K210

- SiFive HiFive Unleashed

# How to get involved with RISC-V International?

- <u>Become a member</u>

- Individuals and non-profits can join free of cost

- RISC-V Technical wiki landing page is the single best place to visit

- Technical Working Groups

- Recently Ratified Extensions

# How to get involved with RISC-V International?

- RISC-V mailing list server

- Only <u>RISC-V members</u> can participate

- Archives of all the lists are public

- <u>Technical Meetings Calendar</u>

- Many groups have bi-weekly or monthly meetings

- o ICS File / Google Calendar

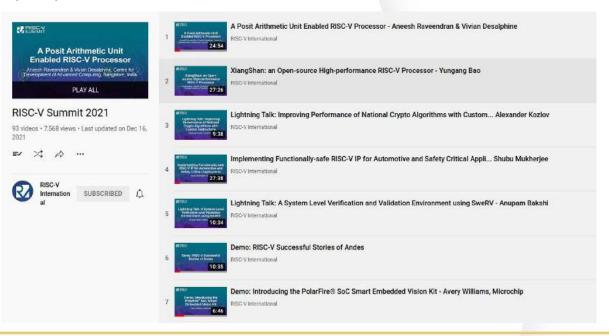

## RISC-V Summit 2021

YouTube playlist with 93 talks

# RISC-V Spring Week 2022

- Videos on the <u>RISC-V YouTube channel</u>

- State of the Union & the Road Ahead

- Maturing the RISC-V Ecosystem

- <u>Evolving the Role of Software in the RISC-V</u>

<u>Ecosystem</u>

- RISC-V IOMMU Architecture Overview

## **Embedded Linux Conf 2021**

- Initializing RISC-V A Guided Tour for ARM Developers

- Ahmad Fatoum & Rouven Czerwinski, Pengutronix

- Building a Low-key XIP-enabled RISC-V Linux System

- Vitaly Vul, Konsulko AB

- Perf on RISC-V: The Past, the Present and the Future

- Atish Patra & Anup Patel, Western Digital

- "A New user(space): Adding RISC-V Support to Zephyr RTOS" [slides]

- Kevin Hilman & Alexandre Mergnat, BayLibre

# RISC-V meetups around the world

Find more at: <u>community.riscv.org</u>

# **RISC-V Open Hours**

- Bi-weekly virtual meetup for the community to interact in real-time

- Primary focus on RISC-V support in open source software and RISC-V dev boards

- Call for participation is open! No prepared talk or slides required!

- Schedule

- Wednesday, June 8, 7:00 PM (US PDT) which is Thursday morning in Asia

- Wednesday, June 29, 9:00 AM (US PDT) which is early evening in Europe

Slides: <u>tinyurl.com/riscv-kr-22</u>

Baylibre

# Linux on RISC-V

Drew Fustini <a fustini@baylibre.com>

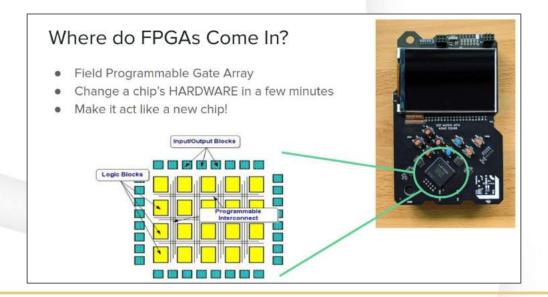

# BONUS: What about RISC-V on FPGAs?

### Introduction

"RISC-V and FPGAs: Open Source Hardware Hacking" keynote at Hackaday Supercon 2019 by Dr. Megan Wachs

# Open source FPGA toolchains

- Project IceStorm for Lattice iCE40 FPGA

- "A Free and Open Source Verilog-to-Bitstream Flow for iCE40 FPGAs" by Claire Wolf

- Project Trellis for the more capable Lattice ECP5 FPGA

- "Project Trellis and nextpnr FOSS FPGA flow for the Lattice ECP5" by Myrtle Shah

- Project X-Ray and <a href="SymbiFlow">SymbiFlow</a> for much more capable Xilinix Series 7

- "Xilinx Series 7 FPGAs Now Have a Fully Open Source Toolchain!" by Tim Ansell

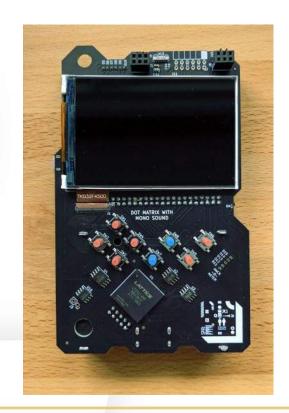

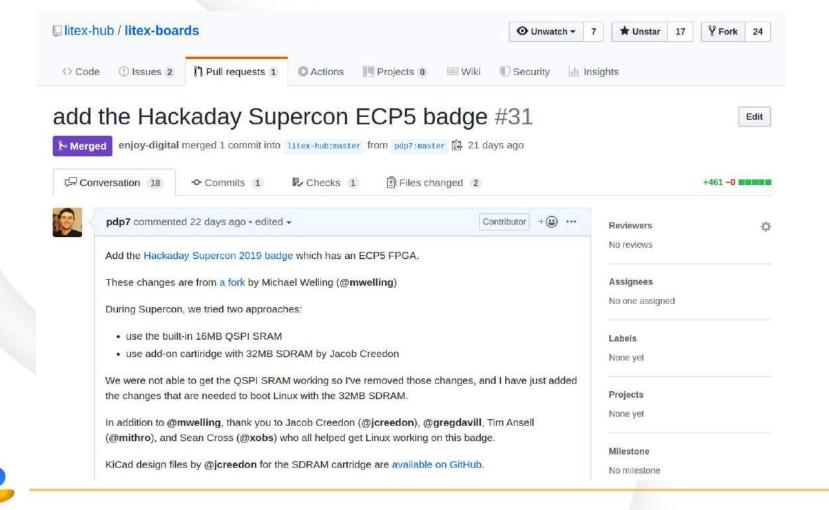

# Hackaday Supercon badge

- RISC-V "soft" core on ECP5 FPGA

- Gigantic FPGA In Game Boy Form Factor

# Why design an SoC in Python?

- Python has advantages over traditional HDL like VHDL and Verilog

- Many people are familiar with Python than HDL (hardware description languages)

- There are currently more software developers than hardware designers

- Migen is a Python framework that can automate chip design

- Leverages the object-oriented, modular nature of Python

- Produces Verilog code so it can be used with existing chip design workflows

## What is Migen?

```

library ieee;

use ieee.std_logic_1164.all;

entity my_module is

clk : in std_logic;

o : out std Logic

architecture rtl of my_module is

signal d : std_logic;

signal q : std_logic;

o <= q;

d <= not q;

process(clk)

if rising_edge(clk) then

d <= q

end if;

VHDL

end rt1;

```

```

migen import *

class MyModule(Module):

def __init__(self):

self.o = Signal()

= Signal()

Signal()

self.comb += [

self.o.eq(q),

d.eq(-q)

self.sync == d.eq(q)

Migen

```

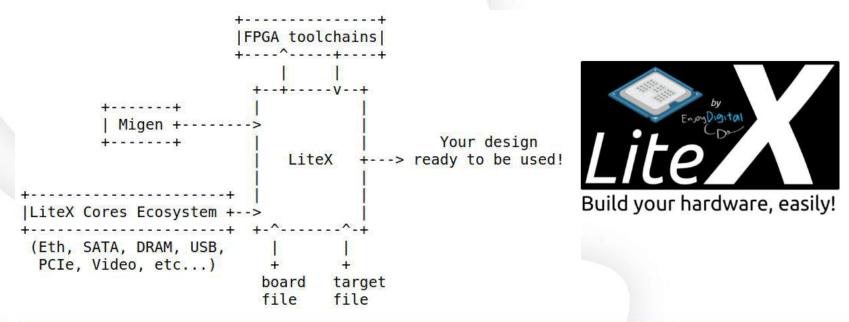

# <u>LiteX</u>

Based on Migen, builds full SoC that can be loaded into an FPGA

# <u>LiteX</u>

- "<u>LiteX vs. Vivado: First Impressions</u>"

- Collection of open cores for DRAM, Ethernet, PCIe, SATA and more...

| Name         | <b>Build Status</b> | Description              |

|--------------|---------------------|--------------------------|

| LiteDRAM     | build passing       | DRAM                     |

| LiteEth      | build passing       | Ethernet                 |

| LitePCle     | build passing       | PCle                     |

| LiteSATA     | build passing       | SATA                     |

| LiteSDCard   | build passing       | SD card                  |

| LitelCLink   | build passing       | Inter-Chip communication |

| LiteJESD204B | build passing       | JESD204B                 |

| LiteVideo    | build unknown       | VGA, DVI, HDMI           |

| LiteScope    | build passing       | Logic analyzer           |

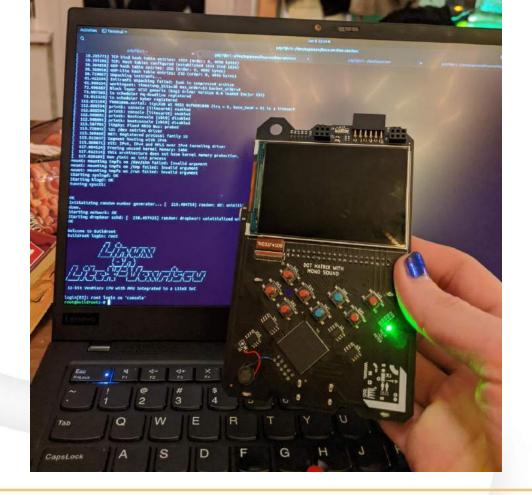

## **Linux on LiteX-VexRiscy**

- <u>VexRiscv</u>: 32-bit Linux-capable RISC-V core

- Designed to be FPGA friendly

- Written in Spinal HDL (based on Scala)

- Builds an SoC using VexRiscv core and LiteX modules

- Such as LiteDRAM, LiteEth, LiteSDCard, LitePCle

- "This project demonstrates how high level HDLs (Spinal HDL, Migen) enable new possibilities and complement each other. Results shown here are the results of a productive collaboration between open-source communities"

- Supports large number of FPGA dev boards including Digilent Arty A7

```

v 215 litex boards/partner/platforms/hadbadge.py

... 00 -0,0 +1,215 00

+ from litex.build.generic_platform import *

2 + from litex.build.lattice import LatticePlatform

6 + _io = [

("clk8", 0, Pins("U18"), IOStandard("LVCMOS33")),

8 +

("programn", 0, Pins("R1"), IOStandard("LVCMOS33")),

9 +

("serial", 0,

10 +

Subsignal("rx", Pins("U2"), IOStandard("LVCMOS33"), Misc("PULLMODE=UP")),

11 +

Subsignal("tx", Pins("U1"), IOStandard("LVCMOS33")),

12 +

13 +

("led", 0, Pins("E3 D3 C3 C4 C2 B1 B20 B19 A18 K20 K19"), 10Standard("LVCMOS33")), # Anodes

("led", 1, Pins("P19 L18 K18"), IOStandard("LVCMOS33")), # Cathodes via FET

14 +

15 +

("usb", 0,

16 +

Subsignal("d_p", Pins("F3")),

Subsignal("d_n", Pins("G3")),

17 +

Subsignal("pullup", Pins("E4")),

18 +

19 +

Subsignal("vbusdet", Pins("F4")),

20 +

IOStandard("LVCMOS33")

21 +

22 +

("keypad", 0,

23 +

Subsignal("left", Pins("G2"), Misc("PULLMODE=UP")),

24 +

Subsignal("right", Pins("F2"), Misc("PULLMODE=UP")),

```

```

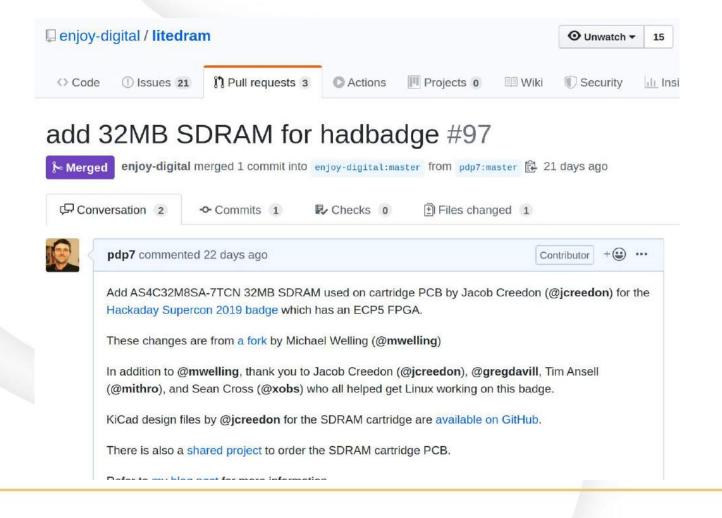

∨ 9 ■■■■■ litedram/modules.py 🚉

***

000 -190,6 +190,15 000 class AS4C32M16(SDRAMModule):

213

technology_timings = _TechnologyTimings(tREFI=64e6/8192, tWTR=(2, None), tCCD=(1, None), tRRD=None)

speedgrade_timings = {"default": _SpeedgradeTimings(tRP=18, tRCD=18, tWR=12, tRFC=(None, 60), tFAW=None, tRAS=None

+ class AS4C32M8(SDRAMModule):

194 +

memtype = "SDR"

195 +

# geometry

196 +

nbanks = 4

197 +

nrows = 8192

198 +

ncols = 1024

199 +

# timings

200 +

technology_timings = _TechnologyTimings(tREFI=64e6/8192, tWTR=(2, None), tCCD=(1, None), tRRD=(None, 15))

201 +

speedgrade_timings = {"default": _SpeedgradeTimings(tRP=20, tRCD=20, tWR=15, tRFC=(None, 66), tFAW=None, tRAS=44)}

ΣĮЗ

```

Now you can enjoy watching Linux boot while outside!!

No PC tether required.

6:05 AM · Feb 22, 2020 · Twitter for iPhone

https://twitter.com/GregDavill/status/1231082623633543168

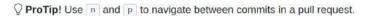

# Open Source ECP5 FPGA boards

- Radiona.org ULX3S

- 32MB SDRAM; ESP32 on-board for WiFi and Bluetooth; \$115 on <u>CrowdSupply</u> or <u>Mouser</u>

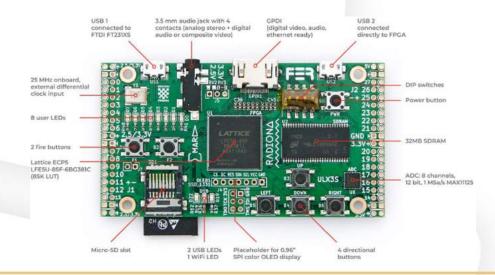

# Open Source ECP5 FPGA boards

- OrangeCrab by Greg Davill

- 128MB DDR RAM; Adafruit Feather form factor; available for \$129

# Want to learn FPGAs? Try Fomu!

- Online workshop from Tim Ansell and Sean Cross

- \$50 on CrowdSupply

- Fits inside USB port!

- Learn how to use:

- MicroPython

- Verilog

LiteX